Una domanda che tutti si pongono è cosa accadrà se o, più probabilmente, quando, la Cina, in qualche modo, rivendicherà realmente l’isola di Taiwan e con essa la TSMC, la silicon foundry che produce la grande maggioranza dei chip di tutto il mondo in tecnologia sia medio-bassa, sia alta-altissima.

Ammettendo che la Cina non rientri in possesso di Taiwan entro il 2027, secondo la società di analisi Voronoi, il mercato dei semiconduttori avanzati entro i prossimi tre anni vedrà una marginale evoluzione in cui, nonostante un crescita di Stati Uniti e Corea, oltre il 60% del mercato resterà appannaggio di Taiwan mentre la Cina, che pure ha avviato decine di small foundry a 30 nm, vedrebbe una diminuzione di market share dall8% al 6%.

In ogni caso l’Europa risulterà assente da questo mercato, nel 2027 come oggi. D’altronde i costi di ingresso del settore sono altissimi; una silicon foundry avanzata costa oggi due volte una portaerei e il costo di avvio è solo l’inizio perché, dopo un paio d’anni, non è già più all’avanguardia e richiede aggiornamenti costosissimi e dai risultati finali non sempre certi.

L’AI, il controllo statale e la nuova guerra digitale

Il settore bellico promette di essere un nuovo protagonista nel futuro dei chip alimentato dall’onnipresente intelligenza artificiale. Il nuovo scenario di guerra reale con missili, sottomarini e droni è, infatti, sempre più paragonabile a quello della cybersecurity in cui un certo numero di endpoint viene continuamente controllato in maniera proattiva sia per le azioni da compiere, sia per i controlli di sicurezza. Dal punto di vista tecnico, infatti, uno smartphone, un semaforo o una lavatrice sono endpoint così come lo sono un drone o un missile. Se, quindi, uno smartwatch può eseguire un modello di AI ottimizzato, può farlo anche un missile o un drone sul campo di guerra.

Tuttavia, il processo produttivo all’interno di una fabbrica di chip comprende migliaia di passaggi nella complessa filiera per passare dalle materie prime al prodotto utilizzabile industrialmente. Il livello di complessità è tale da rendere impossibile per una singola entità statale controllare l’intera filiera. Non a caso la Russia ha abbandonato il settore mentre la Cina, che pure ha una strategia di elevato controllo e investimento, perde, come visto, terreno. Lo stesso Pentagono deve affidarsi a produttori esterni per la produzione di chip da utilizzare in ambito bellico.

La scommessa dei chiplet

Uno delle strade che l’Occidente sta seguendo per cercare di allontanarsi dal dominio assoluto della taiwanese TSMC (impegnata in una faticosa migrazione all’estero per evitare drammi in caso di riassorbimento alla Cina) e anche della sudcoreana Samsung, che grandemente si è avvantaggiata negli ultimi anni è di far leva sulla tecnologia dei chiplet.

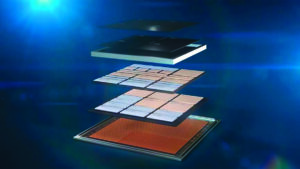

Nei chip che conosciamo, le varie aree funzionali sono interconnesse in modo vario. Per vari motivi, però, le varie funzioni (CPU, GPU, memoria, sensori, modem) evolvono in maniera diversa e richiedono ciascuna una sua ottimizzazione. Un filone tecnologico ha quindi ritenuto opportuno ridurre le singole funzioni a piccoli chip, i chiplet appunto, che possono poi essere inseriti in un’unica piastrina con sistemi di interconnessione diversi da quelli di integrazione quindi di semiconduttore puro. Oltre che per motivi squisitamente tecnologici, i chiplet sono uno dei modi nei quali è possibile modificare lo status quo nella produzione di chip: cambiando la filiera si rischia di più, ma si può provare a cambiare il mercato.

Rientra in questo business anche la Silicon Box, azienda di Singapore con alle spalle tanta storia (Marvell, tra l’altro), che ha recentemente annunciato l’apertura su suolo italiano di una fabbrica di assemblaggio di chiplet.

L’importanza delle tecniche di packaging

Interconnessione e assemblaggio sono un’altra delle aree in cui l’innovazione tecnologica può contribuire a spostare la geopolitica del mondo.

Anche dal punto di vista dell’assemblaggio c’è la moderna esigenza di integrare in un unico scatolino, in maniera efficiente (per molti parametri), componenti di tipo diverso: chip/chiplet analogici e digitali, memorie di vario tipo, sensori in ingresso e uscita, modulatori/demodulatori.

È questo un punto sul quale c’è grande competizione non solo da parte dei soliti noti come TSMC, Samsung e la stessa Intel, ma anche con la Silicon Box di italico interesse. Anche Siemens spinge molto sulla standardizzazione.

I processi di packaging sui quali si discute oggi sono, tra gli altri, Foveros, CoWos e inFO. Nel dettaglio Intel punta su Foveros ed EMIB (dopo FCBGA 2D), TSMC su vari approcci tra cui inFO, Samsung propone CoWoS, Silicon Box al momento punta su FCBGA. Alcune proposte cinesi sono SMIC/FlipChip, Huawei/WLCSP, ma esistono anche altre soluzioni.

Discontinuità tecnologica per cambiare la geopolitica

Per cambiare la geopolitica serve discontinuità mentre il continuo progresso dei vari processi è di natura evolutiva e non crea discontinuità.

Il packaging crea discontinuità e quindi offre rischi ed opportunità ma, oltre al packaging, creano discontinuità le generazioni di macchinari e ancor prima le fisiche alternative.

Per i macchinari si parla spesso di ASML, la multinazionale olandese fondata nel 1984 e specializzata nello sviluppo e nella produzione di macchine per fotolitografia utilizzate per produrre chip.

Il gruppo olandese (ma con un panorama di aziende controllate e una filiera enormi) negli ultimi dieci anni ha saputo “andare oltre la fisica” e, in qualche modo, oggi realizza macchinari che “illuminano” selettivamente le aree di silicio, indicando dove deporre materiale e dove no.

Intel, che ha le sue fabbriche, perse il vantaggio competitivo sul resto del mondo quando non seguì ASML mentre TSMC lo fece. Ora è il suo turno di arrivare prima con il sistema litografco di nuova generazione da 350 milioni di euro basato sulla tecnologia High-NA di extreme ultra-violet light (di fatto raggi X) e sviluppato proprio insieme ad ASML. Resta da chiedersi cosa succederebbe se ASML fosse acquisita da organizzazioni statunitensi (o cinesi).

Per le “altre fisiche” basterà citare la presunta esposizione multipla fatta da Huawei per raggiungere funzionalità da 7nm con macchinari da 14 nm oppure l’idea cinese di incidere direttamente i semiconduttori con un sincrotrone: si può fare, certo, ma non conviene, non è scalabile ed è difficile farne un ecosistema.

La dimensione dei transistor lascia spazio ai nodi

È opinione diffusa che una delle chiavi di aumento delle prestazioni dei chip sia la riduzione delle dimensioni dei suoi singoli elementi, i transistor. È questa una visione molto semplicistica del problema, anche considerando la fisica di quello che continuiamo a chiamare transistor.

Commercialmente la identifichiamo come la larghezza del singolo transistor misurata in nanometri, ovvero miliardesimi di metro. Oggi si parla di 2 o 3 nm per i chip avanzatissimi, 4-7 nm per quelli avanzati e 10-30 nm per la maggior parte del mercato.

Al riguardo della dimensione del transistor viene solitamente evocata la Legge di Moore, che nella sua forma giornalistica ipotizza il dimezzamento dell’area attiva di un transistor ogni 18/24 mesi. Orbene, quand’anche questa legge sia stata vera per un certo periodo, non è direttamente utilizzabile per processi di produzione diversi tra loro, nei quali i transistor e le aree attive sono molto diverse: i 3 nm di Samsung sono diversi dai 3 nm di TSMC e di Intel. Ecco perché oggi si preferisce astrarre il transistor e parlare di nodi.

Questione di chimica

I chip possono essere caratterizzati anche in base alla chimica del semiconduttore lavorato sopra al disco di silicio che funge da sostrato.

Tradizionalmente si usa il silicio anche per disegnare le funzioni. Storicamente il primo materiale fu il germanio, che ancor oggi ha le sue applicazioni, mentre più recentemente si sono affermati altri materiali a base di indio o gallio. In particolare, unendo silicio e germanio otteniamo il carburo di silicio, in inglese silicon carbide, un semiconduttore particolarmente importante nelle situazioni che devono sopportare un flusso significativo di corrente. Per le applicazioni di potenza, dai condizionatori ai motori elettrici, il SiC offre numerosi e sensibili vantaggi nel ciclo di vita del prodotto. E poiché la trasformazione elettrica è quasi ovunque, questa sostanza ha un grande rilievo per il futuro dell’Europa, che punta a produrre elettrodomestici e auto sempre più elettriche.

Le 3 dimensioni dei chip

I chip oggi possono essere suddivisi in tre grandi categorie.

I chip propriamente detti sono dispositivi di varia dimensione che sono lavorati come tessere di un disco di silicio da 20 o 30 cm di diametro.

I wafer-scale (full o half) sono cluster di chip che usano l’intero disco con un numero elevato di chip già interconnessi e che vengono usati come elaboratore unico. Al mondo ci sono pochi modelli di questi dispositivi di cui il più famoso è certamente il Cerebras, giunto alla versione 3.

I chiplet, invece, sono tessere provenienti da lavorazioni diverse che vengono poi impacchettate in un unico contenitore. A differenza dei chip le cui aree sono connesse direttamente su silicio e inserite in package relativamente semplici, nei chiplet, le stesse aree funzionali sono fisicamente separate e poi connesse esternamente e inserite in package complessi.